Pipelined FFT IP Core

The Pipelined FFT IP Core provides efficient continuous data FFT calculations at the rate of one point per clock cycle.

Used in both FPGA and ASIC devices, and excellent for applications where low memory usage is desired. Can result in the least ASIC area usage because of low memory requirement for medium to long FFT lengths.

We provide cores for Xilinx and Altera FPGAs (using inferred block RAM and their math IP cores for floating point applications), as well as provide ASIC-targeted or FPGA-to-ASIC roadmap cores (using SRAM wrappers and our own fixed or floating point math cores).

Used in both FPGA and ASIC devices, and excellent for applications where low memory usage is desired. Can result in the least ASIC area usage because of low memory requirement for medium to long FFT lengths.

We provide cores for Xilinx and Altera FPGAs (using inferred block RAM and their math IP cores for floating point applications), as well as provide ASIC-targeted or FPGA-to-ASIC roadmap cores (using SRAM wrappers and our own fixed or floating point math cores).

Key Features

Key features of the pipelined FFT IP Core.

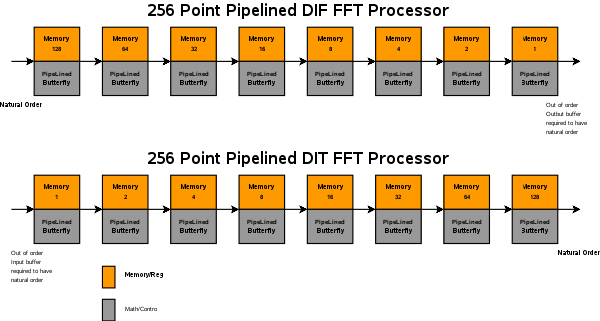

Block diagram showing pipelined rank structure with local memories.

- Any radix-2 length

- Variable length option for runtime per-transform length select

- Clock rates to 400MHz in Virtex-5

- Fixed or floating point math

- Efficient memory usage, useful for ASIC applications

- Continuous data processing

- Optimized butterfly structure in each rank, consumes and produces one point per clock cycle

- Decimation-in-Frequency (DIF) has normal order input, out of order output

- Decimation-in-Time (DIT) has out of order input, normal order output.

- Optional input or output buffer, for completely normal order I/O

Block diagram showing pipelined rank structure with local memories.

Block Diagram

Block diagram showing pipelined rank structure with local memories.

Architecture Specific Implementations

Device Fit Estimate or Additional Information

Fill out the FFT IP Fit/Information Form to obtain a device usage estimate in your target technology or to obtain additional information about a specific FFT architecture.