Dillon Ingenuity

At DE, advanced capabilities enable ingenious solutions. One definition of ingenuity is "cleverness in design". This implies doing things a little differently, such that the outcome is more proficiently and efficiently achieved. Perhaps this is inventing something from scratch. Or maybe just applying something existing in a way that hadn't been done before.

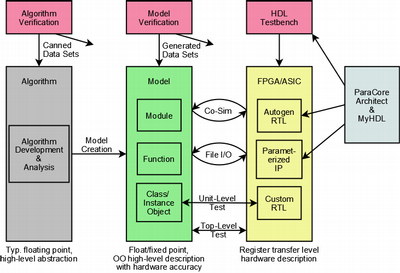

At Dillon Engineering, we have developed capabilities that go beyond the standard design flow. In this age of larger logic devices, more complex applications, yet more tenuous design schedules, our expertise in higher-level code generation, modeling and verification makes the difference in productivity and precision. When looking to engage a design team that truly gets it and knows how to get there from here better than the others, look no further than Dillon Engineering.

Visit the following for examples of Dillon ingenuity in action.

At Dillon Engineering, we have developed capabilities that go beyond the standard design flow. In this age of larger logic devices, more complex applications, yet more tenuous design schedules, our expertise in higher-level code generation, modeling and verification makes the difference in productivity and precision. When looking to engage a design team that truly gets it and knows how to get there from here better than the others, look no further than Dillon Engineering.

Visit the following for examples of Dillon ingenuity in action.

- HDL auto-generation capabilities with our internally-developed ParaCore Architect tool.

- High-level language modeling for fast and accurate algorithm representation.

- Robust verification techniques for streamlined, comprehensive model and HDL simulation.

- Fixed vs Floating Point for addressing the issues of floating point to fixed point conversion.

- Fixed Point Math for detailing fixed point math formats and operations.