Parallel Butterfly FFT

Parallel butterfly structure for multiple point (rank-at-a-time) processing performance

The Parallel Butterfly FFT IP Core provides efficient continuous data FFT calculations at the rate of multiple points per clock cycle. A bank of parallel butterflies executes the FFT one rank at a time on multiple I/O streams.

The Parallel Butterfly FFT IP Core provides efficient continuous data FFT calculations at the rate of multiple points per clock cycle. A bank of parallel butterflies executes the FFT one rank at a time on multiple I/O streams.

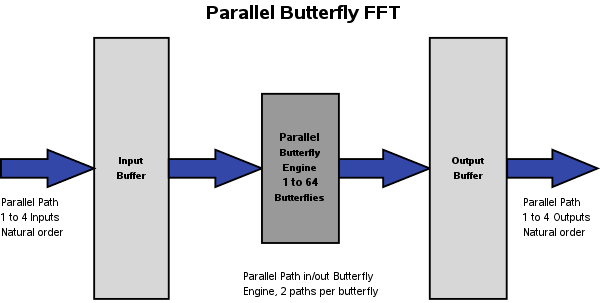

Block Diagram

Block diagram of the Parallel Butterfly FFT:

Key Features

- ParaCore Architect parametric-based core provides maximum adaptability and flexibility (see details on the FFT Parameters)

- Completely proven in many real-world applications

- Supports any radix-2 length FFT and IFFT transformations

- Variable length option for runtime per-transform length select

- Fixed- or floating-point complex I/O of any width

- Integrated Hanning Window (user defined)

- Optional magnitude output

- Designed for continuous transformations with extremely fast conversion times

- Naturally ordered I/O streams

- Parallel I/O paths for maximum throughput

- Massively parallel butterfly architecture, from 1 butterfly up to the full logic capacity of the target device.

- Available in generic HDL or targeted EDIF formats

- Delivered as a completely self contained module with a full testbench

Additional Information

Our FFT core is based on radix-2 reduction, which results in a very efficient implementation capable of any power-of-2 length FFT or IFFT (see also our FFT Datasheet or our Floating Point FFT Factsheet).

A sample of the FFT ParaCore parameters used to build the DE FFT IP Core.

Please feel free to contact us with any FFT core questions or comments.

A sample of the FFT ParaCore parameters used to build the DE FFT IP Core.

Please feel free to contact us with any FFT core questions or comments.

Device Fit Estimate or Additional Information

Fill out the FFT IP Fit/Information Form to obtain a device usage estimate in your target technology or to obtain additional information about a specific FFT architecture.