When to Hire Dillon Engineering?

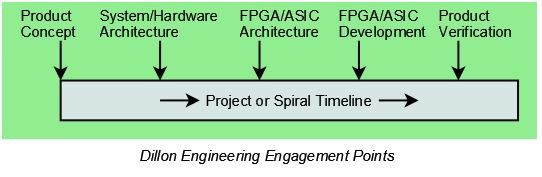

It is never too early or too late to engage Dillon Engineering on your critical project timeline.

Dillon's engineering force is ready to integrate with your team and use our services to assist or carry the ball in whatever capacity you require. From start to completion, your project can leverage our expertise at any crucial stage along the way. Refer to the following example project timeline.

Dillon's engineering force is ready to integrate with your team and use our services to assist or carry the ball in whatever capacity you require. From start to completion, your project can leverage our expertise at any crucial stage along the way. Refer to the following example project timeline.

Count on Dillon Engineering during your project's phases:

- Product Concept. When your ideas, algorithms, or legacy systems are being envisioned as high performance end products, we can investigate feasibility, perform trade studies, and develop high-level architecture alternatives that will begin moving your ideas toward realization.

- System/Hardware Architectures. As the system requirements are solidified, count on our knowledge of processing technologies and state-of-the-art COTS vendor offerings to assist in developing your system architecture. We can investigate high-level partitioning, performance predictions, system throughput, heterogeneous processing, and FPGA/ASIC feasibility in your system.

- FPGA/ASIC Architecture. As your system is partitioned into custom logic processing elements, solid chip architectures are the key to getting required performance under system constraints. We know how best to utilize the available device and IP resources (hard and soft) to move forward with efficient, elegant logic designs.

- FPGA/ASIC Development. Driving the logic designs to completion is our bread and butter. Our standard IP building blocks, internally developed ParaCore Architect tool, and sophisticated modeling environment all contribute to our solid logic design flow. We are proficient with the operation and expectations of back-end tools for synthesis and device routing.

- Product Verification. Our robust modeling and simulation processes are what ensures that your hardware behaves as intended, without hidden bugs keeping checkout tied up for weeks.